Freecell - Verilog Implementation

GitHub RepositoryDescription

Implemented a fully functional Freecell solitaire card game in Verilog,

designing digital logic to manage card states, game mechanics, and player interactions.

Used ModelSim to design and simulate the complex game logic, ensuring correct behavior

for card movement validation, win condition detection, and game state transitions.

Developed the HDL architecture to handle actual gameplay, implementing features such as

free cell storage, tableau management, and foundation pile logic. This project demonstrated

proficiency in hardware design principles, simulation methodologies, and the ability to

translate complex algorithmic concepts into efficient digital logic.

Start Screen

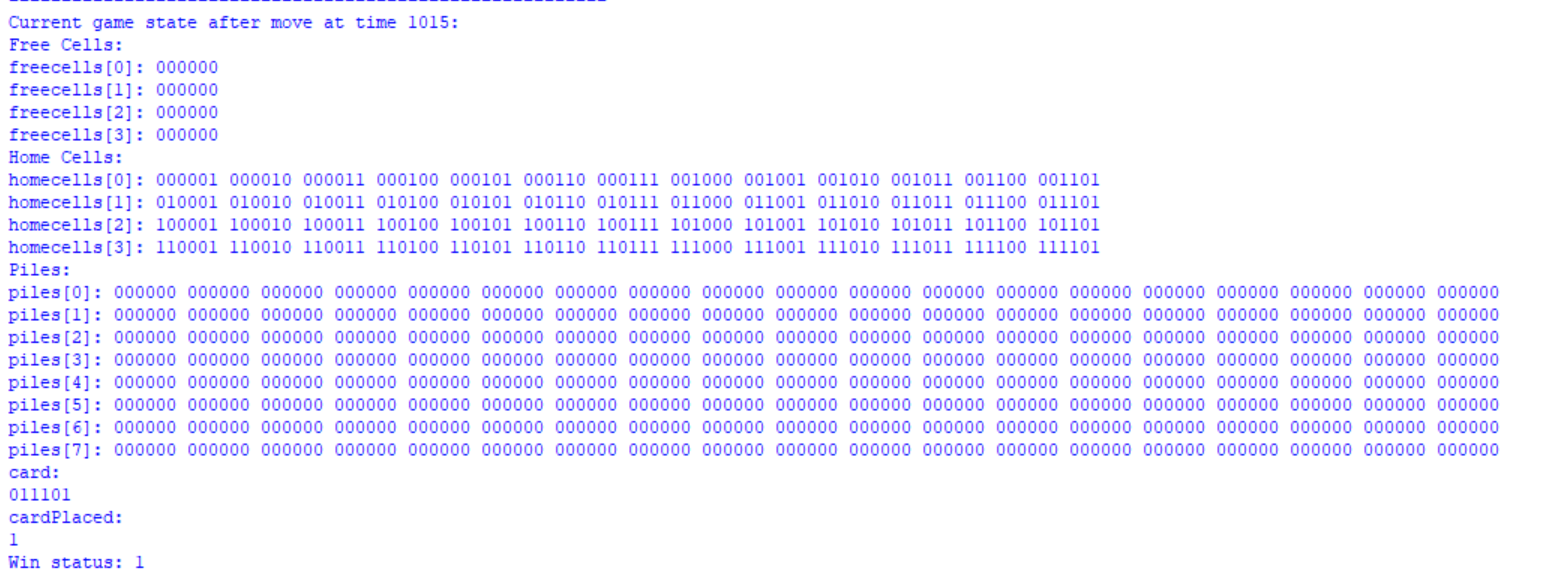

Initial game state

image

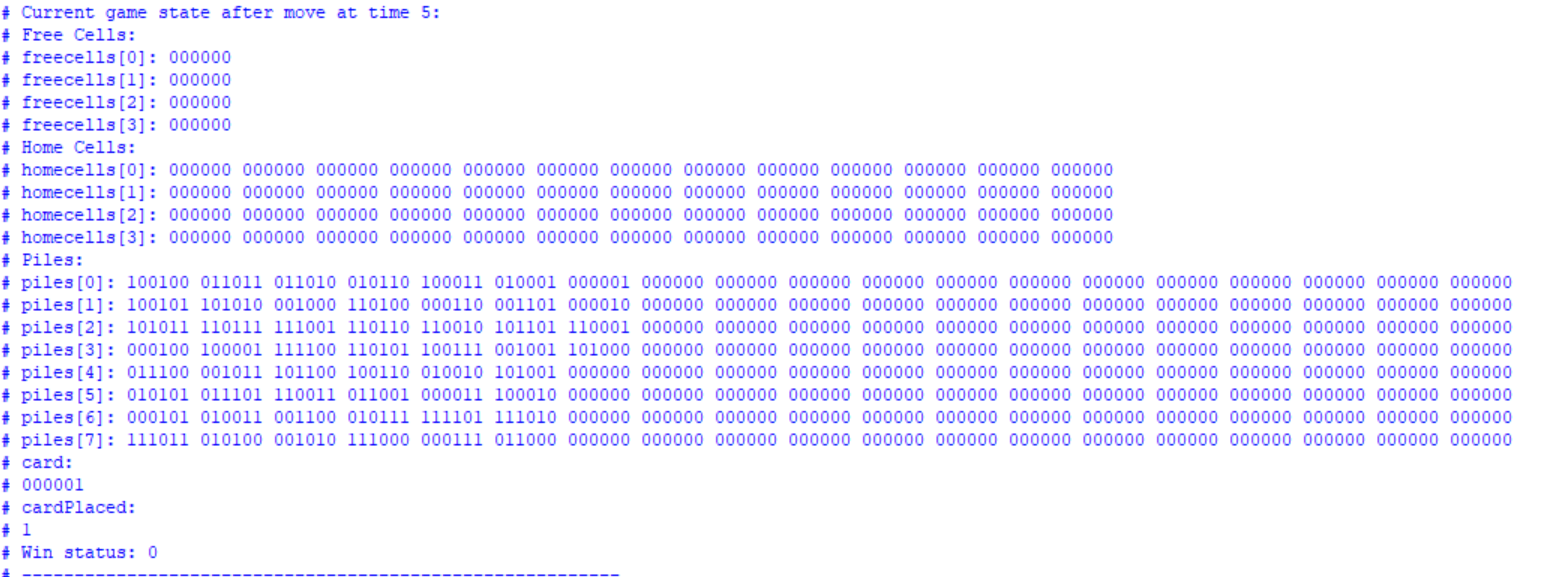

Midgame

Game in progress

image

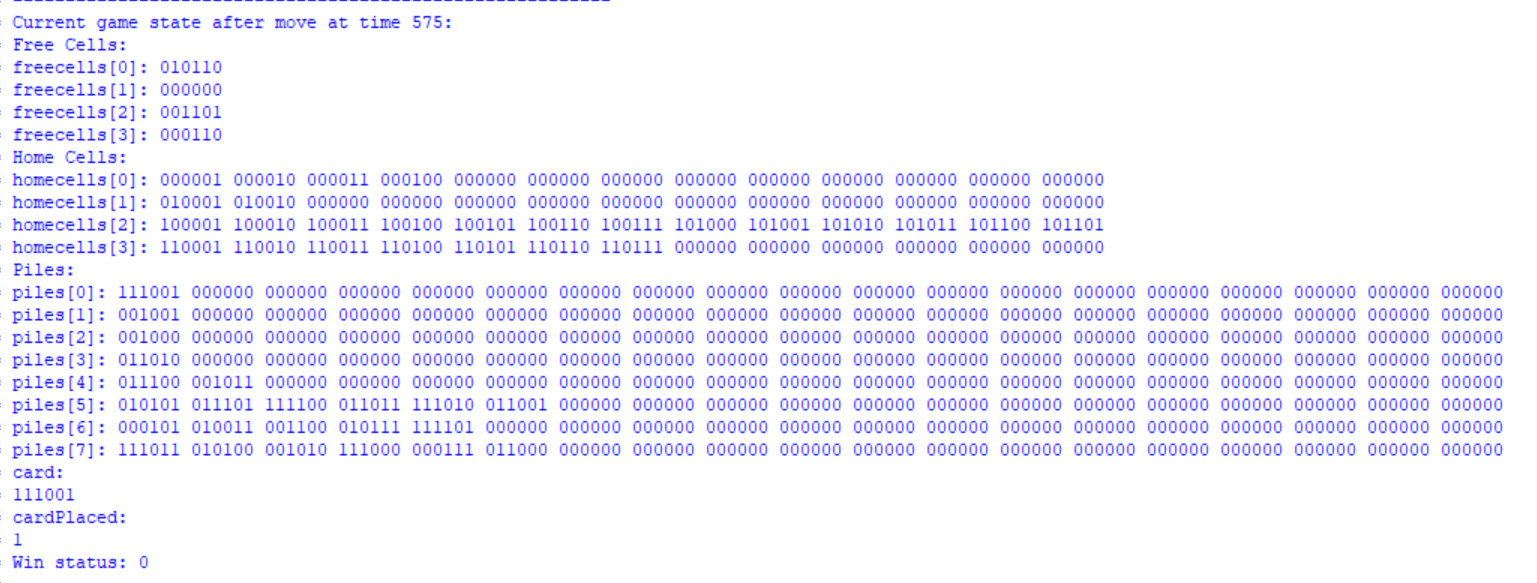

Win Screen

Victory screen

image